晶振

晶振起振条件

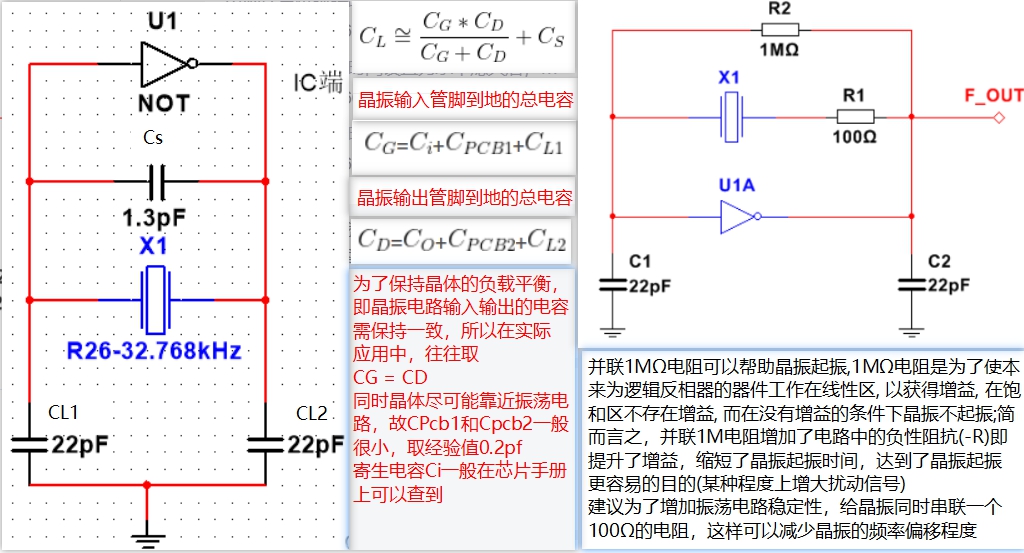

补充:并联电阻不能太小,串联电阻不能太大。否则,在温度较低的情况下不易起振 1MΩ电阻适用于以下问题: 当发生程序启动慢或不运行时,建议给晶振并联1MΩ的电阻 在低温环境下振荡电路阻抗也会发生变化,当阻抗增加到一定程度时,晶振就会发生起振困难或不起振现象。这时,我们也需要给晶振并联1MΩ电阻

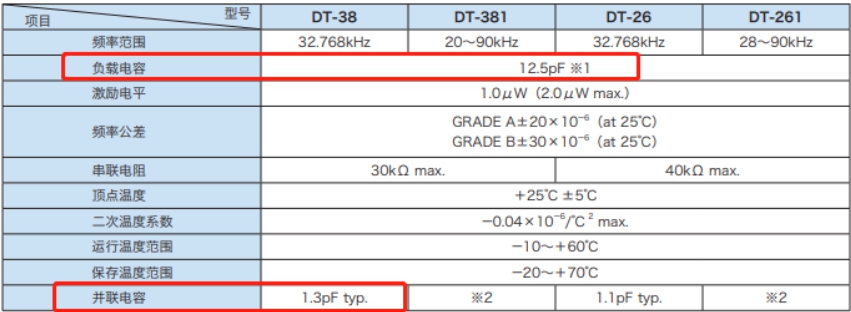

晶振参数以及匹配电容的计算

负载电容

\[C_{L}\cong\frac{C_{G}*C_{D}}{C_{G}+C_{D}}+C_{S}\]

即负载电容跟晶体振荡电路输入管脚到GND的总电容CG 、晶体振荡电路输出管脚到GND的总电容CD以及晶体本身的并联电容CS有关。

我们知道晶体振荡电路输入管脚到GND的总电容一般由以下几部分组成,即: 1. 需要外加晶振的单片机或其他IC管脚到GND之间的寄生电容Ci; 2. 振荡输入端OSC_IN的PCB走线到GND之间的寄生电容Cpcb1; 3. 电路上额外需要增加的并联到GND的外匹配电容 CL1

\[C_{G}=C_{i}+C_{PCB1}+C_{L1}\] 同样的,晶体振荡电路输出管脚到GND的总电容一般由以下几部分组成,即: 1. 需要外加晶振的单片机或者其他IC管脚到GND之间的寄生电容 Co 2. 振荡输出端OSC_OUT的PCB走线到GND之间的寄生电容Cpcb2 3. 电路上额外需要增加的并联到GND的外匹配电容 CL2

\[C_{G}=C_{O}+C_{PCB2}+C_{L2}\]

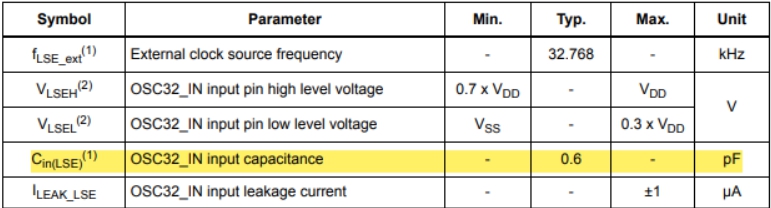

如上所述,我们应该通过需要外接晶振的单片机或者其他IC的资料确认寄生电容Ci和Co

例如:

我们知道,在平时的电路设计中会要求晶体尽可能的靠近振荡电路,即走线尽量短并且对称,所以和 的值应该很小,这里按照经验一般取0.2pF。 为了保持晶体的负载平衡,即晶振电路输入输出的电容需保持一致,所以在实际应用中,往往取CG=CD,故代入公式有:

12.5pf-1.3pf=CG/2=CD/2=11.2pF,即CD=CG=22.4pF

故CL1=CL2=22.4pF-Ci-Cpcb1=22.4pF-0.2pF-0.6pF=21.6pF

故选取22pF作为匹配值

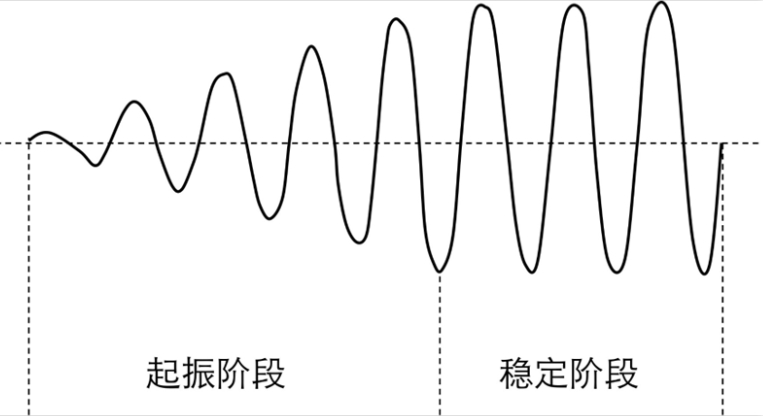

晶振起振的详解

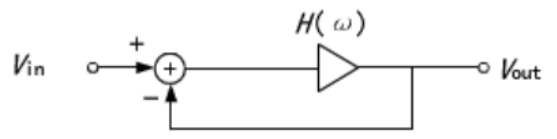

巴克豪森准则:电子振荡器系统信号由输入到输出再反馈到输入的相差为360°,且环路增益≥1,为振荡器起振的必要条件

一个简单振荡器想产生周期性的振荡,通常是以电压形式的输出,在持续不断地输出的同时,需要加入放大器以产生持续的反馈给到输入,由于放大器本身的输出在高频时相移太大会使整个反馈变成正的,从而产生振荡

晶振的观测

示波器

用示波器看波形是最直接的方法。因晶振波形的占空比为50%,所以测得的平均电压为1/2Vcc左右,晶振波形一般是正弦波或者方波,当输出波形是方波时,一般上升沿比较陡峭,且包含了较多的高频信号,这个时候就要保证测试的带宽足够,理论值是带宽是被测信号频率的2倍,实际测试方波时带宽应该是被测信号频率的10倍。 除了带宽之外,在测试晶振时,还有一点应该重点注意:晶振对电容负载较敏感,探头电容相对较大,相当于一个很重的负载并联在晶振电路中,容易导致电路停振而得不出正确的测量结果。所以在进行晶振测试的时候,需要保证足够的带宽和较小的输入电容

万用表

无源晶振具备两个管脚:频率输入脚与频率输出脚。若晶振已经起振,说明这两个管脚之间必然存在电压差,这样才会有流经的电流对晶片产生激励功率。所以,我们可以用万用表的直流电压档,测量晶振两个引脚的电压。起振的时候,晶振两端的电压一般为芯片供电电压Vcc的一半。 但这里要注意,若芯片不良,则无法捕捉到晶振正在提供给它的正确的时钟信号。在这种情况之下,我们容易对晶振是否起振做出误判

频率计

使用频率计测量晶振频率输出脚位时,若有正常的波形(常见为方波,温补晶振有削峰正弦波输出)或正常频率信号输出,则可视为该晶振已经正常起振。

最后,听声音判断晶振是否起振的方法,并不可靠。因为晶体的振荡频率远超人耳能够听见的频率上限,有时能够听到反而是有问题的,说明晶体质量不佳,更多的时候,正常工作的晶体是不会发出任何人耳能听到的声音的,有时声音来自外电路元件

有源晶振的输出引脚接OSC_IN,OSC_OUT悬空